AI SoC設計平台

為支援學術界人工智慧(AI)晶片系統研發,台灣半導體研究中心(TSRI)引進必要矽智產(IP)並建構AI 系統晶片(SoC)設計平台。

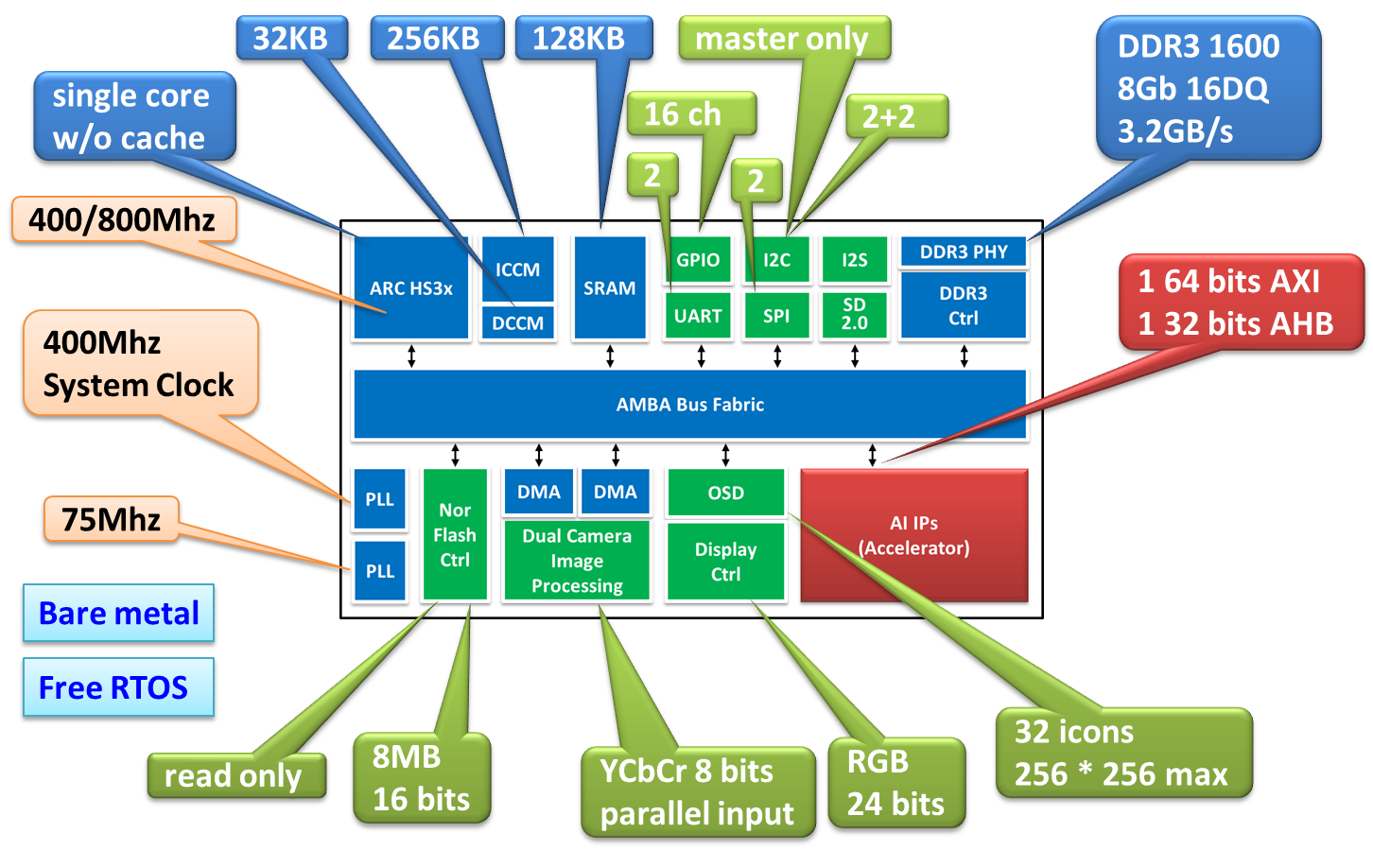

目前TSRI已完成以Synopsys ARC HS3x處理器為核心之SoC設計平台的建構。平台如圖一所示,學界研發團隊可設計AI運算加速電路(紅色區塊)並整合至TSRI AI SoC設計平台為完整SoC。 TSRI則在學界團隊進行設計時,提供必要的技術協助,並在晶片實際下線製作後,協助終端應用系統展示。使用者可依據應用需求增減周邊電路,也可有限度的客製化匯流排。 以下針對平台重要組成電路元件進行說明:

目前TSRI已完成以Synopsys ARC HS3x處理器為核心之SoC設計平台的建構。平台如圖一所示,學界研發團隊可設計AI運算加速電路(紅色區塊)並整合至TSRI AI SoC設計平台為完整SoC。 TSRI則在學界團隊進行設計時,提供必要的技術協助,並在晶片實際下線製作後,協助終端應用系統展示。使用者可依據應用需求增減周邊電路,也可有限度的客製化匯流排。 以下針對平台重要組成電路元件進行說明:

圖一、TSRI ARC HS Based AI SoC Design Platform Block Diagram

-

核心處理器為32位元的ARC HS3x Processor,其被設定為無快取電路的單核心處理器HS34,內建256KB ICCM(Instruction Close Coupled Memory)及32KB DCCM(Data Close Coupled Memory)。Synopsys ARC HS3x Processor資訊請參閱以下網址:

https://www.synopsys.com/dw/ipdir.php?ds=arc-HS34-HS36-HS38 - 匯流排為AMBA AXI/AHB/APB介面,預留給學界設計電路之連接埠包含1個用來傳遞資料的AXI master port,1個用來設定內部暫存器的AHB slave port。使用者可針對終端應用需求與TSRI討論並修改連接埠的數量和資料寬度等匯流排參數。

- 記憶體包括內建的128KB SRAM,外接的DDR 3 1600 DRAM(8Gb/16DQ)以及8MB/16 bits的Nor Flash。

- 作為SoC clock source的PLL輸出預設頻率為400Mhz,使用者可針對終端應用需求與TSRI討論clock規劃。

- 平台內建雙FHD(30fps)影像輸入介面電路及具有OSD功能的HDMI影像輸出介面電路。

- 平台具備I2C、SPI、GPIO、UART、I2S、SD 2.0介面電路。